探秘英特尔酷睿芯片制造工艺:纳米尺度下的性能跃迁与能效优化

- 问答

- 2025-11-06 21:45:00

- 13

(信息主要综合自英特尔官方网站的技术白皮书、历年架构日发布内容以及行业分析师报告)

想象一下,你手中智能手机或笔记本电脑的核心——那块小小的英特尔酷睿处理器,其内部结构比一座现代大都市的规划还要复杂精密千万倍,它的性能强弱和续航时长,直接取决于一个我们肉眼完全无法感知的维度:纳米尺度下的制造工艺,这就像是用一支比头发丝还要细数万倍的“笔”,在指甲盖大小的硅晶圆上,雕刻出数百亿个“建筑物”(晶体管),并让它们以每秒数十亿次的速度协同工作,英特尔近年来在制造工艺上的每一次“跃迁”,其本质就是让这些“建筑物”更小、更密集、更省电,同时开关速度更快。

要理解这种跃迁,首先得知道芯片的“地基”——晶体管,过去很多年,英特尔主导的“鳍式场效应晶体管”(FinFET)技术是行业标准,它通过让电流在像鱼鳍一样竖立的硅片通道中流动,有效控制了漏电问题,但随着尺寸微缩逼近物理极限,鱼鳍的“高度”和“厚度”都难以再优化,这时,英特尔在最新的Intel 20A和18A工艺中,引入了一项革命性的技术: RibbonFET,这被称为“全环绕栅极”(GAA)晶体管的一种实现方式。(来源:英特尔2021年架构日技术详解)你可以把它想象成从单一的“鱼鳍”进化到了多条平行的“纳米片带”,而控制电流的“闸门”从三面包裹变成了360度全包围,这样一来,对于同样大小的区域,英特尔工程师可以在更精细的尺度上控制电流的导通与关闭,就像把水龙头的开关从粗调旋钮换成了极精密的微调阀,既能快速放出大水(高性能),也能精准控制到一滴一滴(高能效),显著降低了功耗。

仅仅有先进的晶体管还不够,连接这数百亿晶体管的,是总长度可达数公里的微缩“导线”,它们就像城市的道路网络,当“建筑物”(晶体管)越来越小、越来越密时,“道路”(互联导线)也会变得更窄、更拥挤,信号传输的延迟和功耗就会成为新的瓶颈,为此,英特尔在制造工艺中率先大规模采用了“背面供电”技术,并将其命名为PowerVia。(来源:英特尔2023年宣布率先在测试芯片上验证PowerVia技术)传统芯片的电力输送和信号传输都在硅片的同一面进行,就像所有电线杆和光纤都挤在同一条马路边,容易互相干扰,PowerVIA技术则像给芯片做了一个“分层设计”:将供电网络从晶体管的“地下室”(硅片背面)送入,而信号传输网络则留在“一楼”(正面),这种“人车分流”式的设计,极大地减少了供电和信号之间的干扰,降低了电压损耗,为芯片在高速运行时的稳定性和能效带来了巨大提升,英特尔表示,这是自“铜互连”技术以来,芯片互联领域最重大的变革。

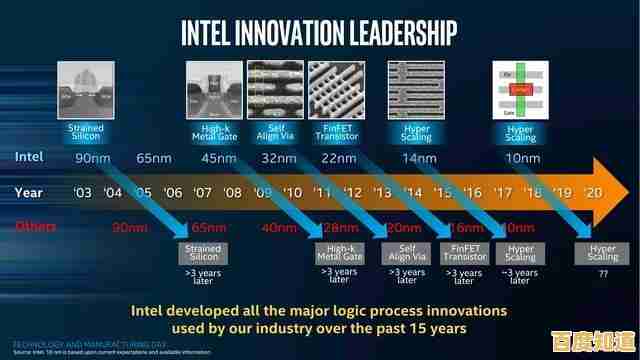

除了这些核心架构的创新,制造工艺的“纳米尺度”本身也在不断缩小,从过去的14纳米、10纳米,到如今的Intel 7、Intel 4,以及未来的Intel 3、20A和18A,每一个数字的减小,都意味着晶体管密度的大幅增加。(来源:英特尔公布的工艺路线图)更高的密度意味着在同样大小的芯片里,可以塞进更多的核心、更强大的图形处理单元(GPU)以及专门处理人工智能任务的加速模块(如NPU),这就是为什么新一代的酷睿Ultra处理器能在保持轻薄本长续航的同时,提供前所未有的AI算力,因为制造工艺的进步,使得集成这些异构计算单元成为可能,并能高效地协调它们的工作,将任务分配给最擅长的单元去执行,从而实现整体能效的优化。

英特尔酷睿芯片的性能跃迁与能效优化,并非单一技术的突破,而是一场在纳米尺度上进行的、多战线协同的精密工程,从晶体管结构从FinFET到RibbonFET的根本性变革,到互联技术引入PowerVIA这样的颠覆性方案,再到制造工艺节点本身的持续微缩与密度提升,这些底层技术的集体进步,最终汇聚成用户可感知的体验:电脑速度更快了,玩游戏更流畅了,处理视频和AI应用更得心应手了,而电池的续航时间却可能更长了,这场在微观世界里的极致探索,正是驱动我们数字世界不断向前发展的核心动力。

本文由蹇长星于2025-11-06发表在笙亿网络策划,如有疑问,请联系我们。

本文链接:http://beijing.xlisi.cn/wenda/73203.html